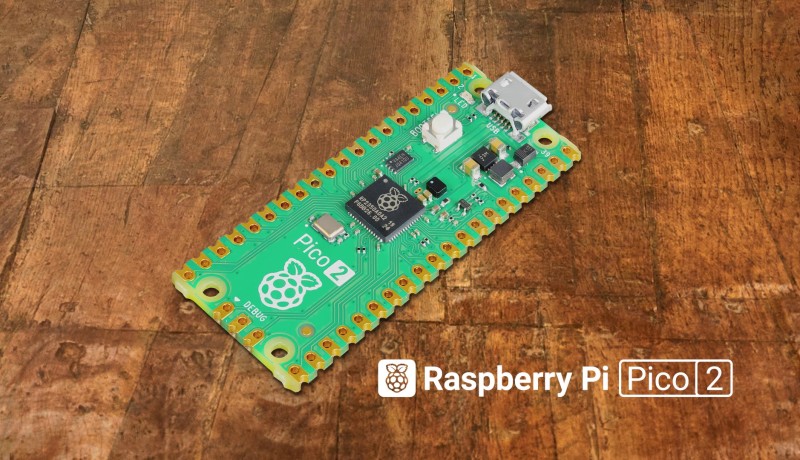

RP2350: The Multicore Chip on the Raspberry Pi Pico 2

on

Compared to the Raspberry Pi RP2040, which was released over three years ago with two M0+ cores, the RP2350 offers significant upgrades. It features double the die size, with a higher core clock speed of 150 MHz, and twice the memory at 520 KB of SRAM across ten banks. The RP2350 also includes new security enhancements. Its die size measures 5.3 mm², in contrast to the 2 mm² of the RP2040. However, the smallest version of the RP2350, the RP2350A, will be only ten cents more expensive, priced at $0.80 in 3,400-unit reels, or $1.10 for single units.

In addition to the M33 cores, the RP2350 introduces two RISC-V cores that can be allocated during the boot process. The boot ROM automatically detects the architecture for a second-stage binary and reboots the chip in the corresponding mode.

The Hazard3 cores, developed by Luke Wren, a Principal Engineer on the Raspberry Pi chip team, were created during his free time using the RISC-V open instruction set architecture (ISA). These cores feature a highly optimized three-stage pipelined processor that implements the RV32I instruction set, along with a broad range of standard extensions focused on enhancing performance and code density. Except for a few security features and the double-precision floating-point accelerator, all aspects of the chip are accessible in RISC-V mode.

This development provides software engineers the opportunity to explore the RISC-V architecture within a stable, well-supported platform, while also promoting Hazard3 as a clean, open core suitable for use in other devices or as a foundation for further innovation, according to the company.

Learn about the Pico 2 in this Elektor article, Raspberry Pi Pico 2: A Powerful New Addition to the Microcontroller Family.

Editor's note: Our colleague Nick Flaherty first reported on this in EENews Europe, a publication in the Elektor network.

Discussion (0 comments)